短溝道效應(yīng)詳解,dibl效應(yīng)分析-KIA MOS管

信息來(lái)源:本站 日期:2025-09-01

短溝道效應(yīng)(short-channel effects)是當(dāng)金屬氧化物半導(dǎo)體場(chǎng)效應(yīng)管的導(dǎo)電溝道長(zhǎng)度降低到十幾納米、甚至幾納米量級(jí)時(shí),晶體管出現(xiàn)的一些效應(yīng)。這些效應(yīng)主要包括閾值電壓隨著溝道長(zhǎng)度降低而降低、漏致勢(shì)壘降低、載流子表面散射、速度飽和、離子化和熱電子效應(yīng)。

在半導(dǎo)體器件設(shè)計(jì)中,短溝道效應(yīng)(ShortChannelEffect,SCE)是指當(dāng)MOSFET的溝道長(zhǎng)度(L)縮小到與耗盡區(qū)寬度相當(dāng)時(shí),器件的電學(xué)特性(如閾值電壓VT、亞閾值擺幅SS、漏電流leakagecurrent等)顯著偏離長(zhǎng)溝道行為的現(xiàn)象。隨著工藝節(jié)點(diǎn)進(jìn)入納米尺度(如5nm、3nm),SCE成為制約器件性能和可靠性的核心挑戰(zhàn)之一。

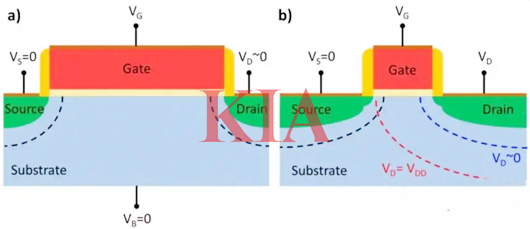

圖1長(zhǎng)溝道(a)和短溝道(b)的MOSFET,虛線(xiàn)表示耗盡區(qū)域

如圖1所示,由源極和漏極擴(kuò)散區(qū)域形成的耗盡區(qū),會(huì)在摻雜最少的結(jié)的一側(cè)延伸,也就是在襯底中延伸。對(duì)于長(zhǎng)溝道晶體管而言,與柵極總長(zhǎng)度相比,這些耗盡區(qū)的延伸可以忽略不計(jì),并且這種影響對(duì)晶體管的電學(xué)特性的作用也微乎其微(圖1.a)。

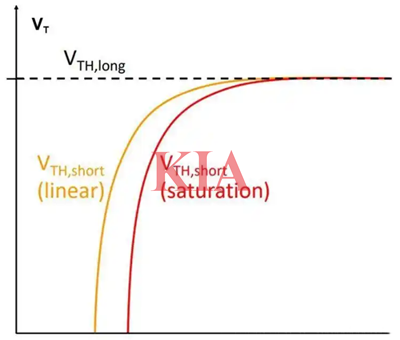

然而,隨著柵極長(zhǎng)度的縮小,耗盡區(qū)的延伸長(zhǎng)度變得與溝道長(zhǎng)度相當(dāng),柵極會(huì)部分失去對(duì)溝道的控制(圖1.b)。結(jié)果,在短溝道長(zhǎng)度下會(huì)出現(xiàn)“閾值電壓滾降(VTHroll-off)”效應(yīng)(圖2.)。

此外,如果在漏極施加偏壓(通常源極接地),漏極擴(kuò)散區(qū)域的耗盡區(qū)會(huì)在溝道內(nèi)進(jìn)一步加深,從而減小有效柵極長(zhǎng)度——溝道長(zhǎng)度調(diào)制效應(yīng),因此在VDS=VGS-VTH以上,電流不會(huì)飽和。當(dāng)VDS值更高時(shí),漏極耗盡區(qū)會(huì)進(jìn)一步延伸到襯底,直至與源極耗盡區(qū)重疊。

因此,在短溝道晶體管中,漏極偏壓會(huì)進(jìn)一步削弱柵極的控制能力。由于強(qiáng)漏極偏壓導(dǎo)致源極/漏極耗盡區(qū)的這種重疊,會(huì)使Source與Bulk結(jié)處的勢(shì)壘降低。由此導(dǎo)致的閾值電壓降低就定義了漏致勢(shì)壘降低(DIBL)效應(yīng)。

總體結(jié)果是,隨著柵極長(zhǎng)度的縮小,閾值電壓降低,當(dāng)晶體管處于飽和區(qū)時(shí),這種現(xiàn)象更為明顯(圖2)。

dibl效應(yīng)

漏致勢(shì)壘降低效應(yīng)(Drain-Induced Barrier Lowering,DIBL)是金屬氧化物半導(dǎo)體場(chǎng)效應(yīng)管(MOSFET)中的重要物理效應(yīng),表現(xiàn)為漏極電壓升高時(shí)源極勢(shì)壘高度降低,導(dǎo)致器件閾值電壓下降。

當(dāng)溝道長(zhǎng)度縮短至納米級(jí)時(shí),漏極耗盡層電場(chǎng)會(huì)穿透至源端區(qū)域,導(dǎo)致源結(jié)勢(shì)壘高度降低,形成柵極無(wú)法控制的漏電流通道。該效應(yīng)直接造成閾值電壓下降和亞閾值電流陡增,導(dǎo)致器件關(guān)斷失效。

聯(lián)系方式:鄒先生

座機(jī):0755-83888366-8022

手機(jī):18123972950(微信同號(hào))

QQ:2880195519

聯(lián)系地址:深圳市龍華區(qū)英泰科匯廣場(chǎng)2棟1902

搜索微信公眾號(hào):“KIA半導(dǎo)體”或掃碼關(guān)注官方微信公眾號(hào)

關(guān)注官方微信公眾號(hào):提供 MOS管 技術(shù)支持

免責(zé)聲明:網(wǎng)站部分圖文來(lái)源其它出處,如有侵權(quán)請(qǐng)聯(lián)系刪除。